I’m looking forward to speaking at DVClub this Thursday. If you are in Austin you can register for free below.

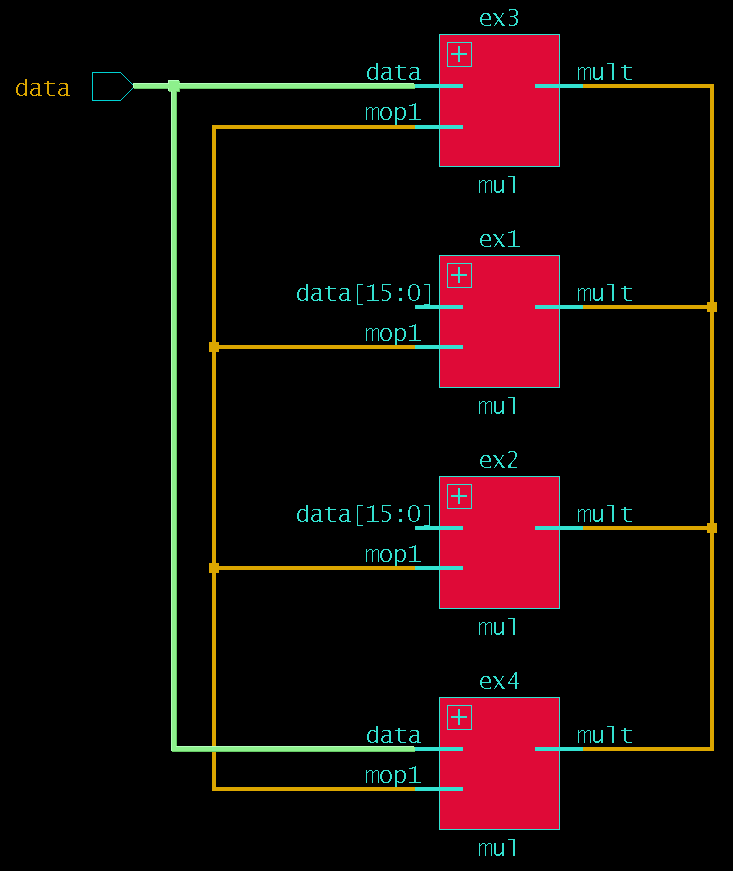

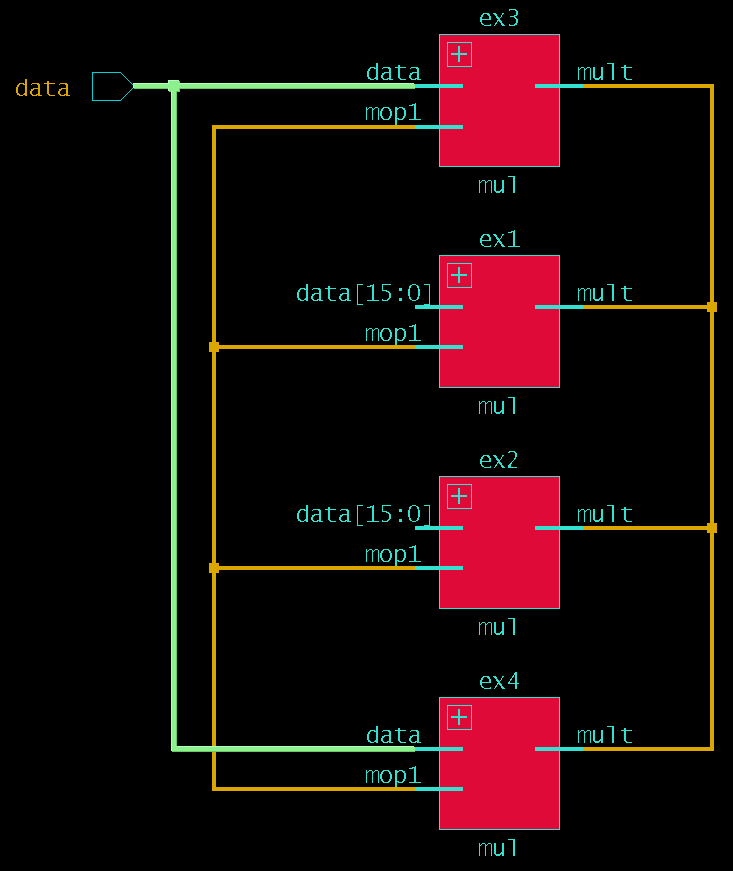

The topic of my talk will be a paper I presented at DVCon 2021 “Can Formal Outsmart Synthesis: Improving Synthesis Quality of Results through Formal Methods”. If you haven’t been to a DVClub event before, you will enjoy it! There is typically a catered lunch and one or two guest speakers. The talks are of general interest and typically touch verification, but sometimes industry topics.

There is a strong emphasis that the talks are more academic and not a push for tools; in full disclosure, I do work at an EDA tool company today, but this talk is a technique that is universal and looks at possible connections between formal and synthesis. I like the topic and hope you will be able to come!

If you wanted to check out the paper of the slides they are linked below.

DVClub Austin, September 28, 2023

11:30 am - 1:30pm

Norris Conference Center

Register