I have been a user of the Tentacle Sync E timecode generator for years now and I love the product. It does exactly what I need and I never had to sync the audio and video in my recordings again. But the mount to the camera was always something I never liked. So I decided to design and build my own.

I am excited to share my latest paper which was recently published at DVCon 2017 in San Jose, California. The full title is:

"Improving Constrained Random Testing by Achieving Simulation Verification Goals through Objective Functions, Rewinding and Dynamic Seed Manipulation"

Abstract

Constrained Random simulation is so critical to modern verification environments that it is a major component of the SystemVerilog language itself. This paper proposes a method that improves how UVM Constrained Random simulations are run. By abstracting the purpose of a simulation to be achieving “Objective Functions” (nominally coverage goals), it is possible to have the simulation autonomously explore deep possibilities from multiple points in time of a standard UVM testbench governed by feedback. This method has a number of benefits including: faster automated coverage closure, an efficient final stimulus solution and proposed higher quality of coverage.

I'm honored to share that my paper:

"Design Patterns by Example for SystemVerilog Verification Environments Enabled by SystemVerilog 1800-2012"

was awarded Best Paper at the Design and Verification Conference (DVCon) 2016. The link to the final paper is now available.

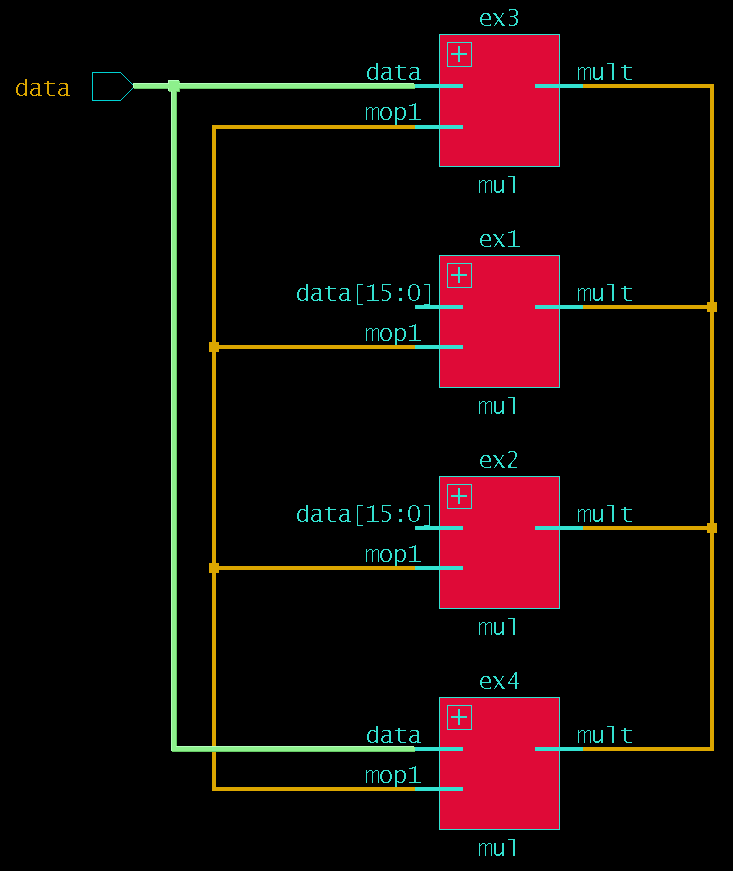

The SystemVerilog bind command allows for adding new functionality to a module. Typically, it is used to add new checking to a RTL block.

I wrote the example code (available on GitHub here) below to demonstrate a feature of bind that allows the binded module to parameterize itself based on where it is being used. When you think about what bind is actually doing it starts to make sense.